## μ**PD720210**

ASSP (USB3.0 Hub CONTROLLER)

ISG-ED1-010002Rev.0.15 Apr. 26, 2012

## 1. OVERVIEW

The  $\mu$  PD720210 is a USB 3.0 hub controller that complies with the Universal Serial Bus (USB) Specification Revision 3.0 and operates at up to 5 Gbps. The device incorporates Renesas' market proven design expertise in USB 3.0 interface technologies and market proven USB 2.0 hub core. The device is fully compatible with all prior versions of USB and 100% compatible with Renesas' industry standard USB 3.0 host controller. It comes in a small 76-pin QFN package and integrates several commonly required external components, making it ideally suited for applications with limited PCB space. In addition, the  $\mu$ PD720210 incorporates Renesas' low-power technologies.

### 1.1 Features

- Compliant with Universal Serial Bus 3.0 Specification Revision 1.0, which is released by USB Implementers Forum, Inc

- Supports the following speed data rate as follows: Low-speed (1.5Mbps) / Full-speed (12Mbps) / High-speed (480Mbps) / Super-speed (5Gbps)

- Supports USB3.0 link power management (U0/U1/U2/U3)

- Supports USB2.0 link power management (LPM: L0/L1/L2/L3)

- Configurable downstream port number of 2/3/4

- Supports all VBUS control

- Individual or Global over-current detection

- Individual or Ganged power control

- Supports downstream port status with LED

- Supports USB3.0/2.0 Compound (non-removable) devices by I/O pin configuration

- Supports clock output (24/12MHz) for Compound (non-removal) device on downstream ports

- Support Energy Star for PC peripheral system

- Single 5V Power Supply

- On chip LDO for 3.3v from 5v input and Switching Regulator for 1.05v from 5v input (TBD)

- System clock: 24 MHz Crystal or Oscillator

- Supports USB Battery Charging Specification Revision 1.2 and other portable devices

- DCP mode of BC 1.2

- CDP mode of BC 1.2

- China Mobile Phone Chargers

- EU Mobile Phone Chargers

- Blackberry, Apple

- Supports Optional SPI ROM

- Vendor ID / Product ID / UUID

- Small Footprint

- Small and low pin count package with simple pin assignment for PCB layout

- Integration of many peripheral components

- Direct routing of all USB signal traces to connector pins only on the top layer

- Automatic switching between Self/Bus-Powered modes

- Integrated Termination resistors for USB

- Fine PHY Controls for Certification

- Pre-emphasis Control (USB3.0)

- Amplitude Adjustment (USB2.0/3.0)

- Provides SUSPEND Status output

## 1.2 Applications

Stand-alone Hub, Monitor-Hub, Docking Station, Integrated Hub, etc.

## 1.3 Ordering Information

| Part Number       | Package            | Remark            |

|-------------------|--------------------|-------------------|

| μPD720210K8-BAF-A | 76-pin QFN (9 × 9) | Lead-free product |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    | $\cdot \circ$     |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   | C.                 |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   | C                  |                   |

|                   |                    |                   |

|                   |                    |                   |

| C                 |                    |                   |

| 0.9               |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

| 80.               |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

|                   |                    |                   |

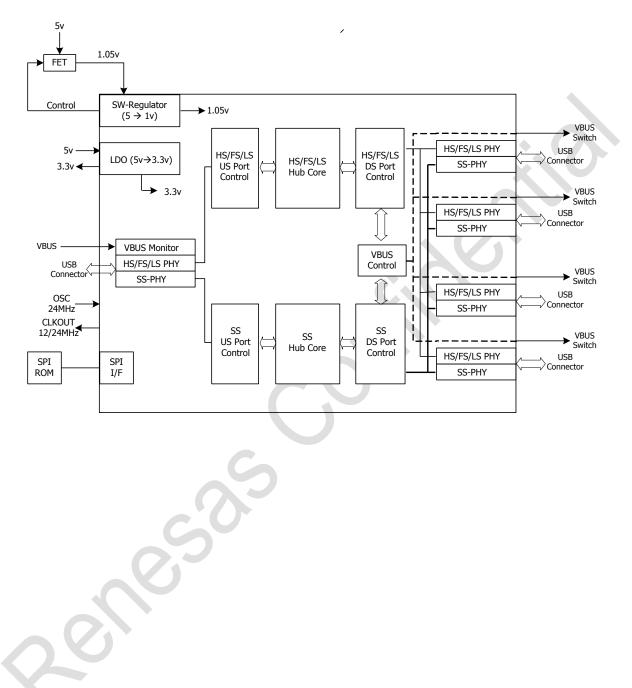

## 1.4 Block Diagram

| Block Name                  | Description                                                                                             |

|-----------------------------|---------------------------------------------------------------------------------------------------------|

| SS PHY                      | For super-speed Tx/Rx                                                                                   |

| HS/FS/LS PHY                | For high-/full-/low-speed Tx/Rx                                                                         |

| Port Power<br>CTL           | The port power (VBUS) on/off control for each port.                                                     |

| VBUS Monitor                | This block monitors the VBUS level of the upstream port.                                                |

| SS US Port<br>Control       | Upstream port control logic for SuperSpeed                                                              |

| HS/FS/LS US<br>Port Control | Upstream port control logic for high-/full-/low-speed                                                   |

| SS Hub Core                 | The central control logic for this SS-Hub system.                                                       |

| HS/FS/LS Hub<br>Core        | The central control logic for this HS/FS/LS Hub system.                                                 |

| SS DS Port<br>Control       | Downstream port control logic for SuperSpeed                                                            |

| HS/FS/LS DS<br>Port Control | Downstream port control logic for HS/FS/LS                                                              |

| VBUS Control                | This block has the top layer of the control of all the port power switcher according to the setting.    |

| SPI Interface               | Connected to external serial ROM which can hold the optional firmware and hu settings                   |

| SW-Regulator                | Switching regulator control logic to output 1.05v power from 5v input, utilizin the external transistor |

| LDO                         | Low DropOut regulator integrated in this hub                                                            |

| 205                         |                                                                                                         |

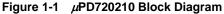

## 1.5 Pin Configuration

• **76-pin QFN (9 × 9)** μPD720210K8-BAF-A

## 2. PIN FUNCTION

This section describes each pin functions.

Strapping Option column in the tables shows the pin can be used to configure the functional settings of this controller when it is pulled up/down. See the related chapter number shown in the column for detail.

## 2.1 Power supply

| Pin Name | Pin No.                                        | I/O<br>Type | Function                             |

|----------|------------------------------------------------|-------------|--------------------------------------|

| VDD10    | 5, 11, 14,<br>22, 28, 31,<br>47, 64, 67,<br>70 | Power       | 1.05V power supply for Core Logic    |

| VDD33    | 8, 17, 25,<br>34, 42, 61,<br>76                | Power       | 3.3V power supply for IO buffer      |

| AVDD33   | 71                                             | Power       | 3.3V power supply for Analog circuit |

| V50IN    | 49                                             | Power       | LDO/SW Regulator 5V Input            |

| V33OUT   | 48                                             | Power       | LDO 3.3V Output                      |

| V33IN    | 50                                             | Power       | SW Regulator 3.3V Input              |

| NGDRV    | 52                                             | -           | SW Regulator Nch FET Control         |

| PGDRV    | 51                                             | -           | SW Regulator Pch FET Control         |

| ILIM     | 53                                             | -           | SW Regulator Current Sense           |

| V10FB    | 54                                             | -           | SW Regulator Output Monitor          |

## 2.2 Analog Interface

| Pin Name | Pin No. | I/O<br>Type | Function                                                                                                      |

|----------|---------|-------------|---------------------------------------------------------------------------------------------------------------|

| RREF     | 72      | -           | Reference Voltage Input for USB2.0 RREF must be connected 1% accuracy of reference resistor of $1.6k\Omega$ . |

## 2.3 System Clock

| Pin Name | Pin No. | I/O<br>Type | Function                                                                                                                             |

|----------|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| XT1      | 74      | IN          | External Oscillator Input<br>Connect to 24MHz crystal<br>or 3V Oscillator input                                                      |

| XT2      | 75      | OUT         | External Oscillator Output<br>Connect to 24MHz crystal<br>In using single-ended clock input to<br>XT1, this pin should be left open. |

## 2.4 System Interface Pins

| Pin Name        | Pin No. | l/O<br>Type | Active<br>Level | Function                                                                                                                 |

|-----------------|---------|-------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|

| SUSPEND/NRDCLKO | 1       | OUT         | High/NA         | SUSPEND Output or CLKOUT                                                                                                 |

| VBUSM           | 43      | IN          | High            | Upstream Port VBUS Monitor                                                                                               |

| BUSSEL          | 44      | IN          | N/A             | Power Mode Select Input<br>0: Bus-power setting<br>1: Self-power setting                                                 |

| LED1B/SUSPEND   | 37      | OUT         | Low             | LED for port1 or SUSPEND Output,<br>depending on pin strap setting of SPICSB.<br>LED for port2 to 4 is described in 2.7. |

| RESETB          | 2       | IN          | Low             | Chip Reset Input                                                                                                         |

## 2.5 USB Port Control Pins

| Pin Name                                     | Pin No.           | I/O<br>Type | Active<br>Level | Function                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|-------------------|-------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OCI1B, OCI2B,<br>OCI3B, OCI4B                | 45, 55,<br>57, 59 | IN          | Low             | Over Current Input<br>0: Over-current condition is detected.<br>1: Non over-current condition is detected.<br>These pins are used for pin strapping<br>option to set non-removal setting.                                                                                                                                                           |

| PPON1B/NRDRSTB,<br>PPON2B, PPON3B,<br>PPON4B | 46, 56,<br>58, 60 | I/O         | Low             | Port Power Control<br>0: Power supply for Vbus is on.<br>1: Power supply for Vbus is off.<br>These pins are used for pin strapping<br>option.<br>PPON4B, PPON3B: Number of Ports<br>PPON2B: Gang/Individual Power Control<br>PPON1B: Clock output enable for on-board<br>Compound (non-removable) Device<br>See µPD720210 User's Manual for detail. |

## 2.6 USB Data Pins

| Pin Name                                    | Pin No.           | І/О<br>Туре | Function                                                   |

|---------------------------------------------|-------------------|-------------|------------------------------------------------------------|

| U3TXDN1,<br>U3TXDN2,<br>U3TXDN3,<br>U3TXDN4 | 4, 13, 21,<br>30  | OUT         | USB3.0 Downstream Transmit data D- signal for super-speed  |

| U3TXDNU                                     | 65                | OUT         | USB3.0 Upstream Transmit data D- signal for<br>super-speed |

| U3TXDP1,<br>U3TXDP2,<br>U3TXDP3,<br>U3TXDP4 | 3, 12, 20,<br>29  | OUT         | USB3.0 Downstream Transmit data D+ signal for super-speed  |

| U3TXDPU                                     | 66                | OUT         | USB3.0 Upstream Transmit data D+ signal for<br>super-speed |

| U3RXDN1,<br>U3RXDN2,<br>U3RXDN3,<br>U3RXDN4 | 7, 16, 24,<br>33  | IN          | USB3.0 Downstream Receive data D- signal for super-speed   |

| U3RXDNU                                     | 68                | OUT         | USB3.0 Upstream Receive data D- signal for<br>super-speed  |

| U3RXDP1,<br>U3RXDP2,<br>U3RXDP3,<br>U3RXDP4 | 6, 15, 23,<br>32  | IN          | USB3.0 Downstream Receive data D+ signal for super-speed   |

| U3RXDPU                                     | 69                | OUT         | USB3.0 Upstream Receive data D+ signal for<br>super-speed  |

| U2DM1, U2DM2,<br>U2DM3, U2DM4               | 10, 19, 27,<br>36 | 1/0         | USB2.0 Downstream D- signal for high-/full-<br>/low-speed  |

| U2DMU                                       | 63                | I/O         | USB2.0 Upstream D- signal for high-/full-/low-<br>speed    |

| U2DP1, U2DP2,<br>U2DP3, U2DP4               | 9, 18, 26,<br>35  | 1/0         | USB2.0 Downstream D+ signal for high-/full-<br>/low-speed  |

| U2DPU                                       | 62                | I/O         | USB2.0 Upstream D+ signal for high-/full-/low-<br>speed    |

## 2.7 SPI Interface

| Pin Name     | Pin No. | I/O<br>Type | Active<br>Level | Function                                                                                                                                                         |

|--------------|---------|-------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPISCK/LED4B | 41      | OUT         | N/A             | External serial ROM Clock Output                                                                                                                                 |

| SPICSB       | 38      | OUT         | Low             | External serial ROM Chip Select<br>This pin is used for pin strap option to<br>select external ROM or LED.                                                       |

| SPISO/LED3B  | 40      | I/O         | N/A             | External serial ROM Data Input (to be<br>connected to Serial Data Output pin of the<br>external ROM) or LED output, depending<br>on pin strap setting of SPICSB. |

| SPISI/LED2B  | 39      | OUT         | N/A             | External serial ROM Data Output (to be<br>connected to Serial Data input pin of the<br>external ROM) or LED output, depending<br>on pin strap setting of SPICSB. |

#### 2.8 Test Pin

| Pin Name | Pin No. | I/O<br>Type | Active<br>Level | Function                        |

|----------|---------|-------------|-----------------|---------------------------------|

| IC(L)    | 73      | IN          | High            | Test Pin to be connected to GND |

# 3. ELECTRICAL SPECIFICATIONS

### 3.1 Buffer List

• 3.3 V input buffer

IC(L)

• 3.3 V input Schmidt buffer

RESETB, OCI2B, OCI3B, OCI4B

• 3.3 V IOLH = 4mA output buffer

SUSPEND/NRDCLKO, SPICSB, PPON1B/NRDRSTB, PPON2B, PPON3B, PPON4B

- 3.3 V IOLH = 12mA output buffer

LED1B/SUSPEND, SPISO/LED2B, SPISCK/LED4B

- 3.3 V IoL = 12mA bi-directional buffer

SPISI/LED3B,

• 5 V input Schmidt buffer

VBUSM, BUSSEL, OCI1B

• • 3.3 V oscillator interface

XT1, XT2

- USB Classic interface

- U2DP(4:1, U), U2DM(4:1, U), RREF

- USB Super-speed Serdes (Serializer-Deserializer)

U3TXDP(4:1, U), U3TXDN(4:1, U), U3RXDP(4:1, U), U3RXDN(4:1, U)

LDO Interface

V33OUT, V50IN

Switching Regulator Interface

V33IN, PGDRV, NGDRV, ILIM, V10FB

## 3.2 Terminology

| Parameter            | Symbol                                                           | Meaning                                                                                                                                                        |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage | V <sub>DD33</sub> ,<br>V <sub>DD10</sub> ,<br>AV <sub>DD33</sub> | Indicates the voltage range within which damage or reduced reliability will not result when power is applied to a VDD pin.                                     |

| Input voltage        | VI                                                               | Indicates voltage range within which damage or reduced reliability will not result when power is applied to an input pin.                                      |

| Output voltage       | Vo                                                               | Indicates voltage range within which damage or reduced reliability will not result when power is applied to an output pin.                                     |

| Output current       | lo                                                               | Indicates absolute tolerance values for DC current to prevent<br>damage or reduced reliability when current flows out of or into<br>output pin.                |

| Storage temperature  | T <sub>stg</sub>                                                 | Indicates the element temperature range within which damage or<br>reduced reliability will not result while no voltage or current is<br>applied to the device. |

| Table 3-1 | Terms Used in Ab | solute Maximum Ratings |

|-----------|------------------|------------------------|

|-----------|------------------|------------------------|

| Parameter                | Symbol                                                           | Meaning                                                                                                                                                                      |

|--------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply voltage     | V <sub>DD33</sub> ,<br>V <sub>DD10</sub> ,<br>AV <sub>DD33</sub> | Indicates the voltage range for normal logic operations occur when $GND = 0 V$ .                                                                                             |

| High-level input voltage | Vih                                                              | Indicates the voltage, which is applied to the input pins of the device,<br>is the voltage indicates that the high level states for normal operation<br>of the input buffer. |

|                          | C                                                                | * If a voltage that is equal to or greater than the "Min." value is applied, the input voltage is guaranteed as high level voltage.                                          |

| Low-level input voltage  | VIL                                                              | Indicates the voltage, which is applied to the input pins of the device,<br>is the voltage indicates that the low level states for normal operation<br>of the input buffer.  |

| 0                        | 3                                                                | * If a voltage that is equal to or lesser than the "Max." value is applied, the input voltage is guaranteed as low level voltage.                                            |

| Input rise time          | T <sub>ri</sub>                                                  | Indicates the limit value for the time period when an input voltage applied to the input pins of the device rises from 10% to 90%.                                           |

| Input fall time          | T <sub>fi</sub>                                                  | Indicates the limit value for the time period when an input voltage applied to the input pins of the device falls from 90% to 10%.                                           |

| Operating temperature    | T <sub>A</sub>                                                   | Indicates the ambient temperature range for normal logic operations.                                                                                                         |

#### Table 3-2 Terms Used in Recommended Operating Range

#### Table 3-3 Term Used in DC Characteristics

| Parameter                        | Symbol          | Meaning                                                                                                                                              |

|----------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Off-state output leakage current | I <sub>OZ</sub> | Indicates the current that flows from the power supply pins when the rated power supply voltage is applied when a 3-state output has high impedance. |

| Input leakage current            | lı –            | Indicates the current that flows when the input voltage is supplied to the input pin.                                                                |

## 3.3 Absolute Maximum Ratings

| Parameter                    | Symbol                                    | Condition                                  | Rating       | Units |

|------------------------------|-------------------------------------------|--------------------------------------------|--------------|-------|

| Power supply voltage         | V <sub>DD33</sub> ,<br>AV <sub>DD33</sub> |                                            | -0.5 to +4.6 | V     |

|                              | V <sub>DD10</sub>                         |                                            | -0.5 to +1.4 | V     |

|                              | V50IN                                     |                                            | TBD          | V     |

| Input voltage, 3.3 V buffer  | VI                                        | V <sub>I</sub> < V <sub>DD33</sub> + 0.5 V | -0.5 to +4.6 | V     |

| Output voltage, 3.3 V buffer | Vo                                        | V <sub>O</sub> <v<sub>DD33 + 0.5 V</v<sub> | -0.5 to +4.6 | V     |

| Input voltage, 5 V buffer    | VI                                        | V <sub>I</sub> < V <sub>DD33</sub> + 2.5 V | -0.5 to +6.6 | v     |

| Output current               | lo                                        | 4 mA Type                                  | 8            | mA    |

|                              | lo                                        | 12mA Type                                  | 24           | mA    |

| Storage temperature          | T <sub>stg</sub>                          |                                            | -65 to +125  | °C    |

#### Table 3-4 Absolute Maximum Ratings

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameters. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded. The ratings and conditions indicated for DC characteristics and AC characteristics represent the quality assurance range during normal operation.

## 3.4 Recommended Operating Ranges

| Parameter                     | Symbol                                    | Condition      | Min.   | Тур. | Max.                   | Units |

|-------------------------------|-------------------------------------------|----------------|--------|------|------------------------|-------|

| Operating voltage             | V <sub>DD33</sub> ,<br>AV <sub>DD33</sub> |                | 3.0    | 3.3  | 3.6                    | V     |

|                               | V <sub>DD10</sub>                         |                | 0.9975 | 1.05 | 1.1025                 | V     |

| High-level input voltage      | V <sub>IH</sub>                           |                | 2.0    |      | V <sub>DD33</sub> +0.3 | V     |

| Low-level input voltage       | V <sub>IL</sub>                           |                | -0.3   |      | 0.8                    | V     |

| Input rise time               | T <sub>ri</sub>                           | Normal Buffer  | 0      |      | 200                    | ns    |

|                               |                                           | Schmitt Buffer | 0      |      | 10                     | ms    |

| Input fall time               | T <sub>fi</sub>                           | Normal Buffer  | 0      |      | 200                    | ns    |

|                               |                                           | Schmitt Buffer | 0      |      | 10                     | ms    |

| Operating ambient temperature | T <sub>A</sub>                            |                | 0      |      | +70                    | °C    |

#### Table 3-5 Recommended Operating Ranges

#### **DC Characteristics** 3.5

#### Table 3-6 DC Characteristics (VDD33 = $3.3 \text{ V} \pm 10\%$ , VDD10 = $1.05 \text{ V} \pm 5\%$ , TA = $-0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter                 | Symbol          | Condition              | Min.                   | Max. | Units |

|---------------------------|-----------------|------------------------|------------------------|------|-------|

| Off-state output current  | I <sub>OZ</sub> | $VI = V_{DD33}$ or GND |                        | ±10  | μA    |

| Input leakage current     | li -            | $VI = V_{DD33}$ or GND |                        | ±10  | μA    |

| Low-level output voltage  | V <sub>OL</sub> | IOL = 0mA              |                        | 0.1  | V     |

| High-level output voltage | V <sub>OH</sub> | IOH = 0mA              | V <sub>DD33</sub> -0.1 |      | V     |

#### Table 3-7 USB interface block

|                                                                 | Table 3-7           | JSB interface block           |      | 12   |      |

|-----------------------------------------------------------------|---------------------|-------------------------------|------|------|------|

| Parameter                                                       | Symbol              | Conditions                    | Min. | Max. | Unit |

| Output pin impedance                                            | Z <sub>HSDRV</sub>  |                               | 40.5 | 49.5 | Ω    |

| Input Levels for Low-/full-speed:                               |                     |                               |      |      |      |

| High-level input voltage (drive)                                | V <sub>IH</sub>     |                               | 2.0  |      | V    |

| High-level input voltage (floating)                             | V <sub>IHZ</sub>    |                               | 2.7  | 3.6  | V    |

| Low-level input voltage                                         | VIL                 |                               | 5    | 0.8  | V    |

| Differential input sensitivity                                  | V <sub>DI</sub>     | (D+) – (D–)                   | 0.2  |      | V    |

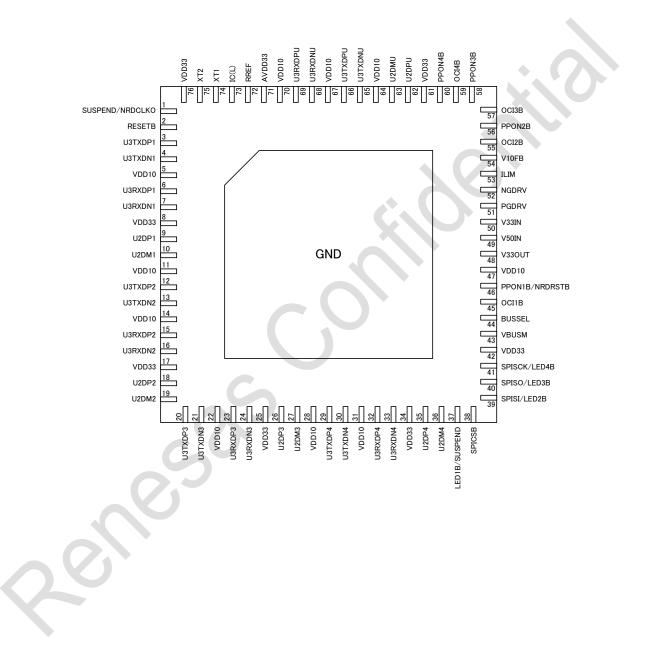

| Differential common mode range                                  | V <sub>CM</sub>     | Includes VDI range            | 0.8  | 2.5  | V    |

| Output Levels for Low-/full-speed:                              |                     |                               |      |      |      |

| High-level output voltage                                       | V <sub>OH</sub>     | RL of 14.25 k $\Omega$ to GND | 2.8  | 3.6  | V    |

| Low-level output voltage                                        | V <sub>OL</sub>     | RL of 1.425 kΩ to 3.6 V       | 0.0  | 0.3  | V    |

| SE1                                                             | V <sub>OSE1</sub>   |                               | 0.8  |      | V    |

| Output signal crossover point voltage                           | V <sub>CRS</sub>    |                               | 1.3  | 2.0  | V    |

| Input Levels for High-speed:                                    |                     |                               |      |      |      |

| High-speed squelch detection threshold (differential signal)    | VHSSQ               |                               | 100  | 150  | mV   |

| High-speed disconnect detection threshold (differential signal) | V <sub>HSDSC</sub>  |                               | 525  | 625  | mV   |

| High-speed data signaling common mode voltage range             | V <sub>HSCM</sub>   |                               | -50  | +500 | mV   |

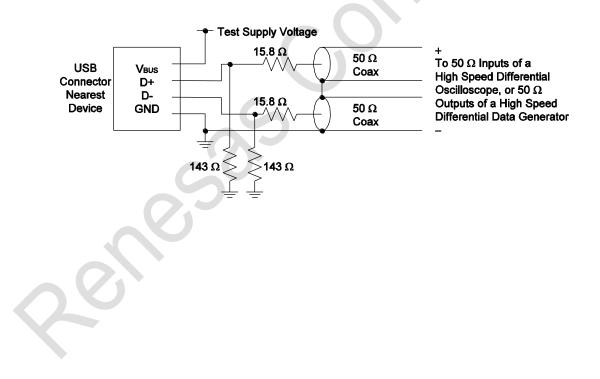

| High-speed differential input signaling level                   | See Figure          | 4-4                           |      |      |      |

| Output Levels for High-speed:                                   |                     |                               |      |      |      |

| High-speed idle state                                           | V <sub>HSOI</sub>   |                               | -10  | +10  | mV   |

| High-speed data signaling high                                  | V <sub>HSOH</sub>   |                               | 360  | 440  | mV   |

| High-speed data signaling low                                   | V <sub>HSOL</sub>   |                               | -10  | +10  | mV   |

| Chirp J level (differential signal)                             | V <sub>CHIRPJ</sub> |                               | 700  | 1100 | mV   |

| Chirp K level (differential signal)                             | V <sub>CHIRPK</sub> |                               | -900 | -500 | mV   |

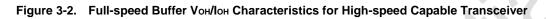

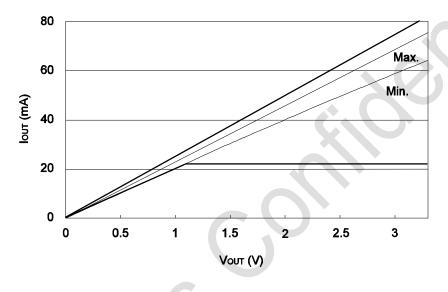

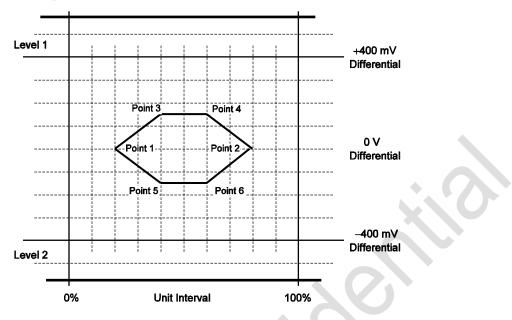

Figure 3-1. Differential Input Sensitivity Range for Low-/full-speed

Figure 3-3. Full-speed Buffer VoL/IoL Characteristics for High-speed Capable Transceiver

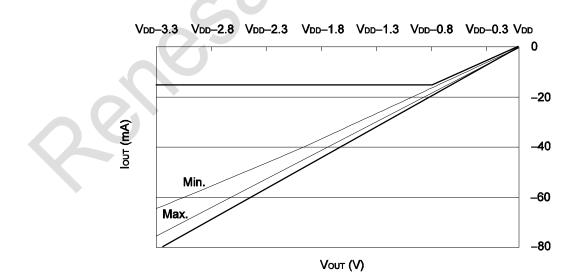

Figure 3-4. Receiver Sensitivity for Transceiver at DP/DM

## 3.6 Pin Capacitance

| Table 3-8 | Pin capacitance    |

|-----------|--------------------|

|           | i ili oupuoliulioo |

| Parameter                     | Symbol           | Condition | Min. | Max. | Units |

|-------------------------------|------------------|-----------|------|------|-------|

| SPI Interface Pin capacitance | C <sub>SPI</sub> |           |      | 5    | pF    |

## 3.7 Sequence for turning on or off power: TBD

## 3.8 AC Characteristics

#### 3.8.1 System Clock

#### Table 3-9 System clock (XT1/XT2) ratings (VDD33 = $3.3 \text{ V} \pm 10\%$ , VDD10 = $1.05 \text{ V} \pm 5\%$ , TA = $-0 \text{ to } +70^{\circ}\text{C}$ )

| Parameter        | Symbol            | Condition | Min.        | Тур. | Max.        | Units |

|------------------|-------------------|-----------|-------------|------|-------------|-------|

| Clock frequency  | F <sub>CLK</sub>  | Crystal   | –100<br>ppm | 24   | +100<br>ppm | MHz   |

| Clock duty cycle | T <sub>DUTY</sub> |           | 40          | 50   | 60          | %     |

**Remark** Required accuracy of crystal or oscillator block includes initial frequency accuracy, the spread of Crystal capacitor loading, supply voltage, temperature and aging, etc.

#### 3.8.2 Reset

Reset and Clock Timing: TBD

#### 3.8.3 USB3.0 SuperSpeed Interface – Differential Transmitter (TX) Specifications

#### (Refer to Universal Serial Bus 3.0 Specification Revision 1.0 for more information)

| Parameter                                                      | Symbol                    | Min    | Max    | Units |

|----------------------------------------------------------------|---------------------------|--------|--------|-------|

| Unit Interval                                                  | UI                        | 199.94 | 200.06 | ps    |

| Differential p-p Tx voltage swing                              | V <sub>TX-DIFF-PP</sub>   | 0.8    | 1.2    | V     |

| Tx de-emphasis                                                 | V <sub>TX-DE-RATIO</sub>  | 3.0    | 4.0    | dB    |

| DC differential impedance                                      | R <sub>TX</sub> -DIFF-DC  | 72     | 120    | Ω     |

| The amount of voltage change allowed during Receiver Detection | VTX-RCV-DETECT            |        | 0.6    | V     |

| AC Coupling Capacitor                                          | CAC-COUPLING              | 75     | 200    | nF    |

| Maximum slew rate                                              | t <sub>CDR-SLEW-MAX</sub> |        | 10     | ms/s  |

| Table 3-10 | Transmitter Normative Electrical Parameters |

|------------|---------------------------------------------|

|            |                                             |

| Table 3-11 | Transmitter Informative Electrical Parameters |

|------------|-----------------------------------------------|

| Parameter                                                 | Symbol                                      | Min   | Max   | Units |

|-----------------------------------------------------------|---------------------------------------------|-------|-------|-------|

| Deterministic min pulse                                   | t <sub>MIN-PULSE-Dj</sub>                   | 0.96  |       | UI    |

| Tx min pulse                                              | t <sub>MIN-PULSE-Tj</sub>                   | 0.90  |       | UI    |

| Transmitter Eye                                           | t <sub>TX-EYE</sub>                         | 0.625 |       | UI    |

| Tx deterministic jitter                                   | t <sub>TX-DJ-DD</sub>                       |       | 0.205 | UI    |

| Tx input capacitance for return loss                      | CTX-PARASITIC                               |       | 1.25  | pf    |

| Transmitter DC common mode<br>impedance                   | R <sub>TX-DC</sub>                          | 18    | 30    | Ω     |

| Transmitter short-circuit current limit                   | I <sub>TX-SHORT</sub>                       |       | 60    | mA    |

| Transmitter DC common-mode voltage                        | VTX-DC-CM                                   | 0     | 2.2   | V     |

| Tx AC common mode voltage                                 | V <sub>TX-CM-AC-PP-</sub>                   |       | 100   | mVp-p |

| Absolute DC Common Mode Voltage between U1 and U0         | V <sub>TX-CM-DC-</sub><br>ACTIVE-IDLE-DELTA |       | 200   | mV    |

| Electrical Idle Differential Peak- Peak<br>Output voltage | V <sub>TX</sub> -IDLE-DIFF-AC-              | 0     | 10    | mV    |

| DC Electrical Idle Differential Output<br>Voltage         | V <sub>TX-IDLE</sub> -DIFF-DC               | 0     | 10    | mV    |

#### 3.8.4 USB3.0 SuperSpeed Interface – Differential Receiver (RX) Specifications

#### (Refer to Universal Serial Bus 3.0 Specification Revision 1.0 for more information)

| Parameter                                                         | Symbol                              | Min    | Max    | Units |

|-------------------------------------------------------------------|-------------------------------------|--------|--------|-------|

| Unit Interval                                                     | UI                                  | 199.94 | 200.06 | ps    |

| Receiver DC common mode<br>impedance                              | R <sub>RX-DC</sub>                  | 18     | 30     | Ω     |

| DC differential impedance                                         | R <sub>RX-DIFF-DC</sub>             | 72     | 120    | Ω     |

| DC Input CM Input Impedance for<br>V>0 during Reset of Power down | Z <sub>RX-HIGH-IMP-DC-</sub><br>POS | 25k    |        | Ω     |

| LFPS Detect Threshold                                             | V <sub>RX-LFPS</sub> -DET-DIFF-     | 100    | 300    | mV    |

|                                                                   | р-р                                 |        |        |       |

#### Table 3-12 Receiver Normative Electrical Parameters

#### Table 3-13 Receiver Informative Electrical Parameters

| Parameter                                                | Symbol                              | Min | Max   | Units  |

|----------------------------------------------------------|-------------------------------------|-----|-------|--------|

| Differential Rx peak-to-peak voltage                     | V <sub>RX-DIFF-PP-POST-</sub><br>EQ | 30  |       | mV     |

| Max Rx inherent timing error                             | T <sub>RX-Tj</sub>                  |     | 0.45  | UI     |

| Max Rx inherent deterministic timing error               | T <sub>RX-DJ-DD</sub>               | 0   | 0.285 | UI     |

| Rx input capacitance for return loss                     | C <sub>RX-PARASITIC</sub>           |     | 1.1   | pF     |

| Rx AC common mode voltage                                | V <sub>RX-CM-AC-P</sub>             |     | 150   | mVPeak |

| Rx AC common mode voltage during the U1 to U0 transition | V <sub>RX-CM-DC-ACTIVE</sub> -      |     | 200   | mVPeak |

| Reines                                                   |                                     |     |       |        |

ISG-ED1-010002 Rev. 0.15 Apr 26, 2012

### 3.8.5 USB2.0 Interface

(1/4)

| Parameter                                                                                                                                                      | Symbol           | Conditions                                      | Min.         | Max.         | Unit     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------|--------------|--------------|----------|

| Low-speed Electrical Characteristics                                                                                                                           |                  |                                                 |              |              |          |

| Rise time (10% to 90%)                                                                                                                                         | tlr              | C∟ = 200 pF to 600 pF                           | 75           | 300          | ns       |

| Fall time (90% to 10%)                                                                                                                                         | t∟F              | C∟ = 200 pF to 600 pF                           | 75           | 300          | ns       |

| Differential rise and fall time matching                                                                                                                       | <b>t</b> lrfm    | (t <sub>LR</sub> /t <sub>LF</sub> ) <b>Note</b> | 80           | 125          | %        |

| Low-speed data rate                                                                                                                                            | <b>t</b> LDRATHS | Average bit rate                                | 1.49925      | 1.50075      | Mbps     |

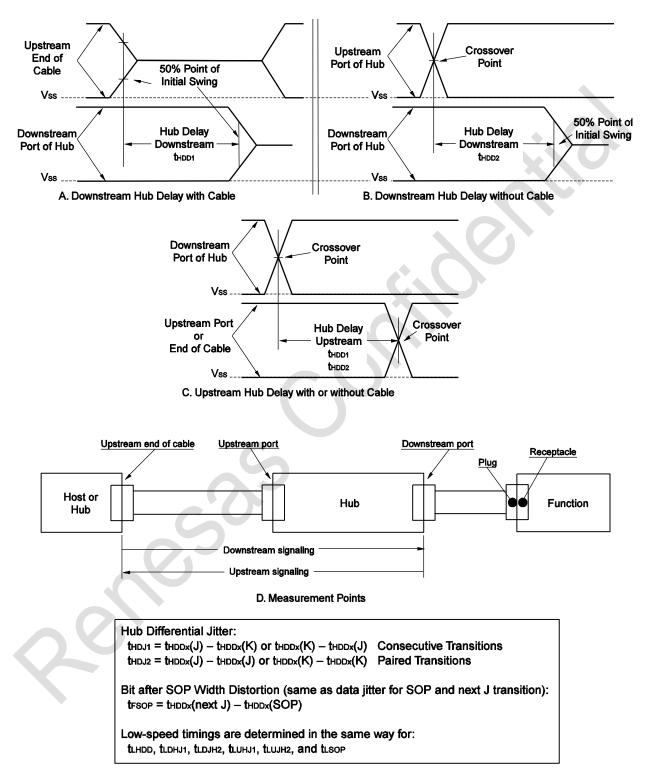

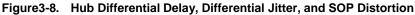

| Downstream facing port source jitter total<br>(including frequency tolerance) ( <b>Figure 3-</b><br><b>10</b> ):<br>To next transition                         | toDJ1            |                                                 | -25          | +25          | ns       |

| For paired transitions                                                                                                                                         | tddj2            |                                                 | -14          | +14          | ns       |

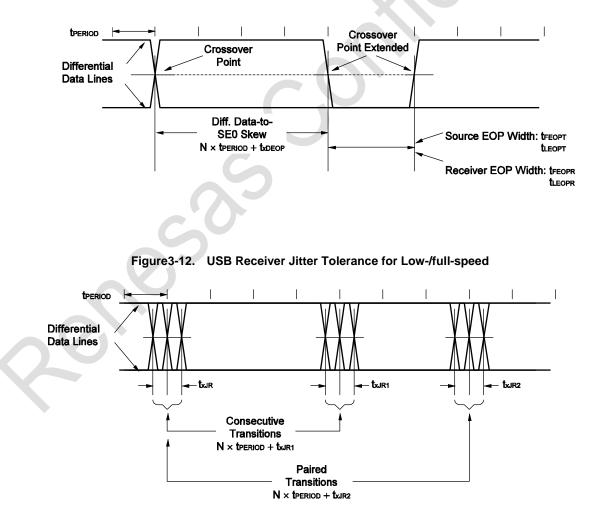

| Downstream facing port differential receiver<br>jitter total (including frequency tolerance)<br>(Figure 3-12):<br>To next transition<br>For paired transitions | tujr1<br>tujr2   | Ś                                               | -152<br>-200 | +152<br>+200 | ns<br>ns |

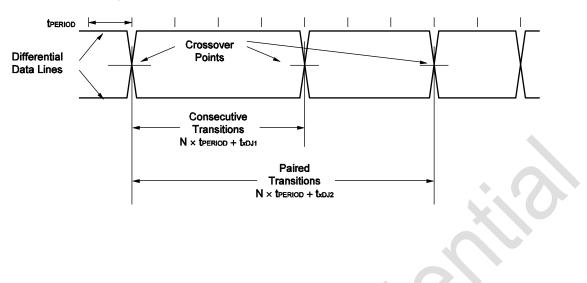

| Source SE0 interval of EOP (Figure 3-11)                                                                                                                       | <b>t</b> leopt   |                                                 | 1.25         | 1.5          | μS       |

| Receiver SE0 interval of EOP (Figure 3-11)                                                                                                                     | <b>t</b> leopr   |                                                 | 670          |              | ns       |

| Width of SE0 interval during differential transition                                                                                                           | t∟s⊤             |                                                 |              | 210          | ns       |

| Hub differential data delay (Figure 3-8)                                                                                                                       | <b>t</b> lhdd    |                                                 |              | 300          | ns       |

| Hub differential driver jitter (including cable) (Figure 3-8):                                                                                                 |                  |                                                 |              |              |          |

| Downstream facing port<br>To next transition<br>For paired transitions                                                                                         | tldhj1<br>tldhj2 |                                                 | -45<br>-15   | +45<br>+15   | ns<br>ns |

| Upstream facing port<br>To next transition<br>For paired transitions                                                                                           | tluhji<br>tluhj2 |                                                 | -45<br>-45   | +45<br>+45   | ns<br>ns |

| Data bit width distortion after SOP (Figure)                                                                                                                   | <b>t</b> lsop    |                                                 | -60          | +60          | ns       |

| Hub EOP delay relative to tHDD (Figure 3-9)                                                                                                                    | <b>t</b> leopd   |                                                 | 0            | 200          | Ns       |

| Hub EOP output width skew (Figure 3-9)                                                                                                                         | <b>t</b> lhesk   |                                                 | -300         | +300         | Ns       |

| Full-speed Electrical Characteristics                                                                                                                          |                  |                                                 |              |              |          |

| Rise time (10% to 90%)                                                                                                                                         | tfr              | CL = 50 pF,<br>Rs = 36 Ω                        | 4            | 20           | ns       |

| Fall time (90% to 10%)                                                                                                                                         | tff              | CL = 50 pF,<br>Rs = 36 Ω                        | 4            | 20           | ns       |

| Differential rise and fall time matching                                                                                                                       | <b>t</b> frfm    | (tfr/tff)                                       | 90           | 111.11       | %        |

| Full-speed data rate                                                                                                                                           | <b>t</b> FDRATHS | Average bit rate                                | 11.9940      | 12.0060      | Mbps     |

| Frame interval                                                                                                                                                 | <b>t</b> FRAME   |                                                 | 0.9995       | 1.0005       | ms       |

**Note** Excluding the first transition from the Idle state.

(2/4)

| Parameter                                                                         | Symbol           | Conditions                  | Min.     | Max.       | Unit     |

|-----------------------------------------------------------------------------------|------------------|-----------------------------|----------|------------|----------|

| Full-speed Electrical Characteristics (Conti                                      | nued)            | •                           |          |            |          |

| Consecutive frame interval jitter                                                 | trfi             | No clock adjustment         |          | 42         | ns       |

| Source jitter total (including frequency tolerance) ( <b>Figure0</b> ):           |                  | Note                        |          |            |          |

| To next transition                                                                | t <sub>DJ1</sub> |                             | -3.5     | +3.5       | ns       |

| For paired transitions                                                            | tDJ2             |                             | -4.0     | +4.0       | ns       |

| Source jitter for differential transition to SE0 transition ( <b>Figure3-11</b> ) | <b>t</b> fdeop   |                             | -2       | +5         | ns       |

| Receiver jitter (Figure3-12):                                                     |                  |                             |          |            |          |

| To Next Transition                                                                | tjr1             |                             | -18.5    | +18.5      | ns       |

| For Paired Transitions                                                            | tjr2             |                             | -9       | +9         | ns       |

| Source SE0 interval of EOP (Figure3-11)                                           | <b>t</b> feopt   |                             | 160      | 175        | ns       |

| Receiver SE0 interval of EOP (Figure3-11)                                         | <b>t</b> feopr   |                             | 82       |            | ns       |

| Width of SE0 interval during differential transition                              | tfst             |                             | X        | 14         | ns       |

| Hub differential data delay (Figure3-8)                                           |                  | C 1                         |          |            |          |

| (with cable)                                                                      |                  |                             |          | 70         | ns       |

| (without cable)                                                                   | thdd2            |                             |          | 44         | ns       |

| Hub differential driver jitter (including cable)                                  |                  |                             |          |            |          |

| (Figure3-8):<br>To next transition                                                | <b>4</b>         |                             | -3       | .0         | 20       |

| For paired transitions                                                            | thdj1<br>thdj2   |                             | -3<br>-1 | +3<br>+1   | ns<br>ns |

| Data bit width distortion after SOP (Figure3-                                     | tFSOP            |                             | -5       | +5         | ns       |

| 8)                                                                                | TESOP            |                             |          | +3         | 115      |

| Hub EOP delay relative to tHDD (Figure 3-9)                                       | <b>t</b> feopd   |                             | 0        | 15         | ns       |

| Hub EOP output width skew (Figure 3-9)                                            | trhesk           |                             | -15      | +15        | ns       |

| High-speed Electrical Characteristics                                             |                  |                             |          |            |          |

| Rise time (10% to 90%)                                                            | thsr             |                             | 500      |            | ps       |

| Fall time (90% to 10%)                                                            | thsp             |                             | 500      |            | ps       |

| Driver waveform                                                                   | See Figure       | 3-7.                        | I        |            |          |

| High-speed data rate                                                              | <b>t</b> HSDRAT  |                             | 479.760  | 480.240    | Mbps     |

| Microframe interval                                                               | thsfram          |                             | 124.9375 | 125.0625   | μS       |

| Consecutive microframe interval difference                                        | tHSRFI           |                             |          | 4 high-    | Bit      |

| <b>NU</b>                                                                         |                  |                             |          | speed      | times    |

| Data source jitter                                                                | See Figure       | 3-7.                        |          |            |          |

| Receiver jitter tolerance                                                         | See Figure       | 3-4 <b>3-4</b> .            |          |            |          |

| Hub data delay (without cable)                                                    | <b>t</b> HSHDD   |                             |          | 36 high-   | Bit      |

| /                                                                                 |                  |                             |          | speed+4 ns | times    |

| Hub data jitter                                                                   | See Figure       | 3-4 <b>3-4</b> , Figure3-7. |          |            |          |

| Hub delay variation range                                                         | tHSHDV           |                             |          | 5 high-    | Bit      |

| ,                                                                                 |                  |                             |          | speed      | times    |

**Note** Excluding the first transition from the Idle state.

(3/4)

| Parameter                                                                                                                 | Symbol           | Conditions                                        | Min.       | Max.          | Unit            |

|---------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|------------|---------------|-----------------|

| Hub Event Timings                                                                                                         |                  |                                                   |            |               |                 |

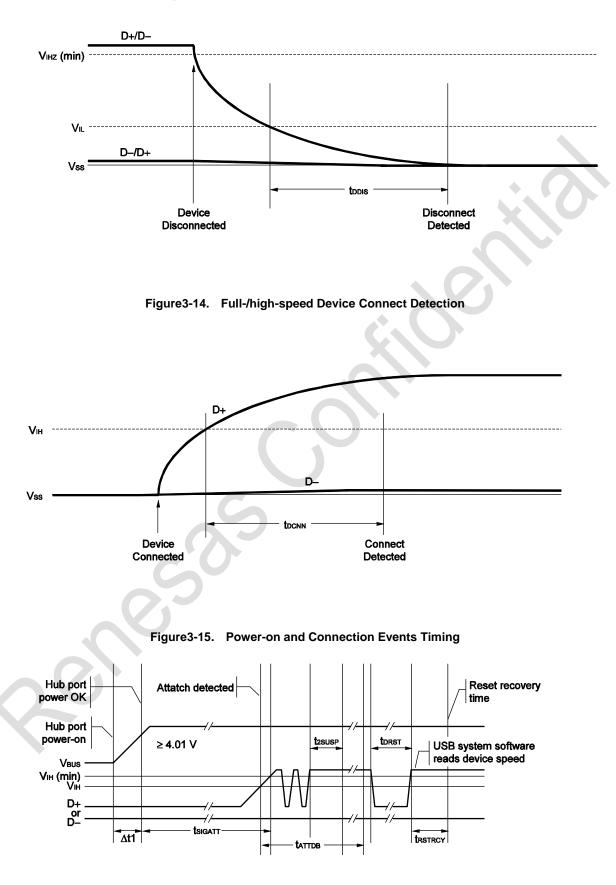

| Time to detect a downstream facing port<br>connect event ( <b>Figure3-14</b> ):<br>Awake hub<br>Suspended hub             | tdcnn            |                                                   | 2.5<br>2.5 | 2000<br>12000 | µs<br>µs        |

| Time to detect a disconnect event at a hub's downstream facing port ( <b>Figure3-13</b> )                                 | todis            |                                                   | 2.0        | 2.5           | μs              |

| Duration of driving resume to a downstream port (only from a controlling hub)                                             | <b>t</b> drsmdn  |                                                   | 20         | +             | ms              |

| Time from detecting downstream resume to rebroadcast                                                                      | <b>t</b> ursm    |                                                   |            | 1.0           | ms              |

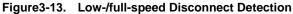

| Duration of driving reset to a downstream facing port ( <b>Figure3-15</b> )                                               | <b>t</b> drst    | Only for a SetPortFeature<br>(PORT_RESET) request | 10         | 20            | ms              |

| Time to detect a long K from upstream                                                                                     | turlk            |                                                   | 2.5        | 100           | μS              |

| Time to detect a long SE0 from upstream                                                                                   | turlse0          |                                                   | 2.5        | 10000         | μS              |

| Duration of repeating SE0 upstream (for<br>low-/full-speed repeater)                                                      | <b>t</b> urpseo  |                                                   | 5          | 23            | FS Bit<br>times |

| Inter-packet delay (for high-speed) of<br>packets traveling in same direction                                             | <b>t</b> HSIPDSD |                                                   | 88         |               | Bit<br>times    |

| Inter-packet delay (for high-speed) of packets traveling in opposite direction                                            | thsipdod         |                                                   | 8          |               | Bit<br>times    |

| Inter-packet delay for device/root hub<br>response with detachable cable for high-<br>speed                               | thsrspipd1       | 5                                                 |            | 192           | Bit<br>times    |

| Time of which a Chirp J or Chirp K must be<br>continuously detected (filtered) by hub or<br>device during Reset handshake | <b>TEILT</b>     |                                                   | 2.5        |               | μS              |

| Time after end of device Chirp K by which<br>hub must start driving first Chirp K in the<br>hub's chirp sequence          | twтосн           |                                                   |            | 100           | μS              |

| Time for which each individual Chirp J or<br>Chirp K in the chirp sequence is driven<br>downstream by hub during reset    | tосныт           |                                                   | 40         | 60            | μS              |

| Time before end of reset by which a hub must end its downstream chirp sequence                                            | tdchse0          |                                                   | 100        | 500           | μS              |

| Time from internal power good to device pulling D+ beyond V <sub>HZ</sub> ( <b>Figure3-15</b> )                           | <b>İ</b> SIGATT  |                                                   |            | 100           | ms              |

| Debounce interval provided by USB system software after attach ( <b>Figure3-15</b> )                                      | <b>t</b> attdb   |                                                   |            | 100           | ms              |

| Maximum duration of suspend averaging interval                                                                            | <b>t</b> susavgi |                                                   |            | 1             | S               |

| Period of idle bus before device can initiate resume                                                                      | twtrsм           |                                                   | 5          |               | ms              |

| Duration of driving resume upstream                                                                                       | <b>t</b> DRSMUP  |                                                   | 1          | 15            | ms              |

(4/4)

| Parameter                                                                                                                                                                                                      | Symbol              | Conditions               | Min. | Max.  | Unit         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|------|-------|--------------|

| Hub Event Timings (Continued)                                                                                                                                                                                  |                     |                          |      |       |              |

| Resume recovery time                                                                                                                                                                                           | trsmrcy             | Remote-wakeup is enabled | 10   |       | ms           |

| Time to detect a reset from upstream for<br>non high-speed capable devices                                                                                                                                     | <b>t</b> DETRST     |                          | 2.5  | 10000 | μS           |

| Reset recovery time (Figure3-15)                                                                                                                                                                               | trstrcy             |                          |      | 10    | ms           |

| Inter-packet delay for full-speed                                                                                                                                                                              | tipd                |                          | 2    |       | Bit<br>times |

| Inter-packet delay for device response with detachable cable for full-speed                                                                                                                                    | trspipd1            |                          |      | 6.5   | Bit<br>times |

| SetAddress() completion time                                                                                                                                                                                   | <b>t</b> dsetaddr   |                          |      | 50    | ms           |

| Time to complete standard request with no data                                                                                                                                                                 | <b>t</b> drqcmpltnd |                          | .0   | 50    | ms           |

| Time to deliver first and subsequent (except last) data for standard request                                                                                                                                   | tdretdata1          |                          |      | 500   | ms           |

| Time to deliver last data for standard request                                                                                                                                                                 | <b>İ</b> DRETDATAN  | X                        |      | 50    | ms           |

| Time for which a suspended hub will see a continuous SE0 on upstream before beginning the high-speed detection handshake                                                                                       | <b>t</b> filtseo    |                          | 2.5  |       | μS           |

| Time a hub operating in non-suspended full-<br>speed will wait after start of SE0 on<br>upstream before beginning the high-speed<br>detection handshake                                                        | twtrstfs            | 5                        | 2.5  | 3000  | ms           |

| Time a hub operating in high-speed will wait<br>after start of SE0 on upstream before<br>reverting to full-speed                                                                                               | <b>İ</b> WTREV      |                          | 3.0  | 3.125 | ms           |

| Time a hub will wait after reverting to full-<br>speed before sampling the bus state on<br>upstream and beginning the high-speed will<br>wait after start of SE0 on upstream before<br>reverting to full-speed | twrrsths            |                          | 100  | 875   | ms           |

| Minimum duration of a Chirp K on upstream from a hub within the reset protocol                                                                                                                                 | tucн                |                          | 1.0  |       | ms           |

| Time after start of SE0 on upstream by<br>which a hub will complete its Chirp K within<br>the reset protocol                                                                                                   | TUCHEND             |                          |      | 7.0   | ms           |

| Time between detection of downstream chip and entering high-speed state                                                                                                                                        | twтнs               |                          |      | 500   | μS           |

| Time after end of upstream Chirp at which<br>hub reverts to full-speed default state if no<br>downstream Chirp is detected                                                                                     | <b>t</b> wtfs       |                          | 1.0  | 2.5   | ms           |

Figure3-6. Transmit Waveform for Transceiver at DP/DM

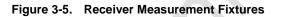

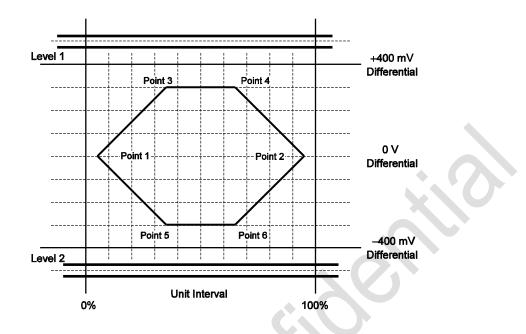

Figure3-7. Transmitter Measurement Fixtures

#### **Timing Diagram**

Figure 3-9. Hub EOP Delay and EOP Skew

Figure3-10. USB Differential Data Jitter for Low-/full-speed

Figure3-11. USB Differential-to-EOP Transition Skew and EOP Width for Low-/full-speed

### **USB3.0 Hub Parameters**

| Name                          | Description                                                                                                                                                                                                                                                                                                                                                                             | Min  | Max  | Units   |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---------|

| tDownLinkStateChange          | Time from receiving the route string of a header<br>packet directed to a downstream port that is in a<br>low power link state to initiating a return to U0 on<br>the downstream link.                                                                                                                                                                                                   | 0    | 100  | ns      |

| sDataSymbolsBabble            | The number of symbols in a data packet payload<br>after the DPPSTART ordered set without and<br>Data Packet Payload ending frame ordered set<br>or DPPABORT ordered set that shall cause a<br>device to detect the packet is invalid.                                                                                                                                                   | 1030 | N/A  | symbols |

| tHubPropRemoteWakeUpstream    | Time from start of remote wakeup signaling on<br>the downstream port a hub to when the hub<br>must propagate the remote wakeup signaling on<br>its upstream port if the upstream port link is in<br>U3.                                                                                                                                                                                 | 0    | 1    | ms      |

| tHubDriveRemoteWakeDownstream | Time from receiving a<br>SetPortFeature(PORT_LINK_STATE) U0 for a<br>downstream port with a link in U3 to driving<br>remote wakeup signaling on the link.                                                                                                                                                                                                                               | 0    | 1000 | ns      |

| tHubPort2PortExitLat          | Time from a downstream port's link initiating a<br>U-state change to when a hub must initiate a U-<br>state change on the upstream port's link (when<br>required).                                                                                                                                                                                                                      | 0    | 1    | μs      |

| aCurrentUnit                  | Unit for reporting the current draw of hub controller circuitry in the hub descriptor.                                                                                                                                                                                                                                                                                                  |      | 4    | mA      |

| nMaxHubPorts                  | Maximum number of ports on a USB 3.0 hub.                                                                                                                                                                                                                                                                                                                                               |      | 15   | Ports   |

| tTimeForResetError            | If the downstream port link remains in<br>RxDetect.active for this length of time during a<br>warm reset, the reset is considered to have<br>failed.                                                                                                                                                                                                                                    | 100  | 200  | ms      |

| tCheckSuperSpeedOnReset       | Time from when a device (not a hub) detects a<br>USB 2.0 bus reset to when the device port must<br>enter the USPORT.Powered-On state.                                                                                                                                                                                                                                                   | 0    | 1    | ms      |

| tUSB2SwitchDisconnect         | Time from when a device (not a hub) enters<br>USPORT.Training to when the device must<br>disconnect on the USB 2.0 interface if the device<br>is connected on USB 2.0.                                                                                                                                                                                                                  | 0    | 1    | ms      |

| tPropagationDelayJitterLimit  | Variation from the minimum time between when<br>the last symbol of a header packet routed to a<br>downstream port with a link in U0 is received on<br>a hub upstream port and when the first symbol<br>of the header packet is transmitted on the hub<br>downstream port. ITP propagation shall meet<br>tPropagationDelayJitterLimit for all downstream<br>ports that transmit the ITP. | 0    | 8    | ns      |

### 3. ELECTRICAL SPECIFICATIONS

| nSkipSymbolLimit | Average number of symbols between | 354 | 354 | Symbols |

|------------------|-----------------------------------|-----|-----|---------|

|                  | transmitted SKP ordered sets.     |     |     |         |

ر ر

### 3.8.6 SPI Type Serial ROM Interface (TBD)

| Table 3-14 SPI Type Serial ROM Interface | Signals Timing (SPI Mode 0) |  |

|------------------------------------------|-----------------------------|--|

|------------------------------------------|-----------------------------|--|

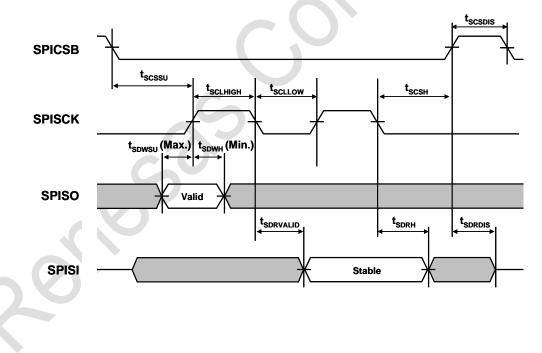

| Parameter                                    | Symbol                    | Min. | Max. | Units |

|----------------------------------------------|---------------------------|------|------|-------|

| SPISCK Clock Frequency                       |                           |      |      | MHz   |

| Clock pulses width Low                       | t <sub>SCLLOW</sub>       |      |      | ns    |

| Clock pulses width high                      | t <sub>SCLHIGH</sub>      |      |      | ns    |

| SPICSB disable time                          | t <sub>SCSDIS</sub>       |      |      | ns    |

| SPICSB setup time                            | t <sub>SCSSU</sub>        |      |      | ns    |

| SPICSB hold time                             | t <sub>SCSH</sub>         |      |      | ns    |

| SPISI setup time to SPISCK rising edge       | t <sub>SDWSU</sub>        |      |      | ns    |

| SPISI hold time from SPISCK rising edge      | t <sub>SDWH</sub>         |      |      | ns    |

| SPISO validate time from SPISCK falling edge | t <sub>SDRVALI</sub><br>D |      |      | ns    |

| SPISO hold time from SPISCK falling edge     | t <sub>SDRH</sub>         |      |      | ns    |

| SPISO disable time from SPICSB disabled      | t <sub>SDRDIS</sub>       |      |      | ns    |

Figure 3-16 SPI Type Serial ROM Signal Timing

## 3.9 Power Consumption (TBD)

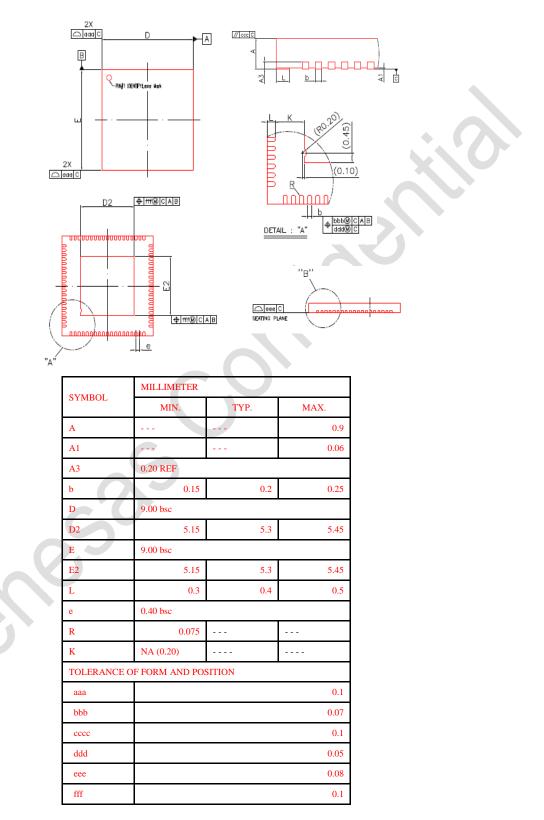

# 4. PACKAGE DRAWINGS

#### • μPD720210K8-BAF-A

76-PIN QFN (9x9)

## **5. RECOMMENDED SOLDERING CONDITIONS**

TBD

**REVISION HISTORY**

### µPD720210 Preliminary Data Sheet

| Rev. | Date           |                      | Description                                            |

|------|----------------|----------------------|--------------------------------------------------------|

|      |                | Page                 | Summary                                                |

| 0.10 | Sept. 30, 2011 | -                    | First Edition issued                                   |

| 0.11 | Oct. 31, 2011  |                      | Pin Name changed. (U2DNx $\rightarrow$ U2DMx)          |

|      |                |                      | Fig. 1-2 Changed. (names of Pin18 and Pin19)           |

| 0.12 | Feb. 21, 2012  |                      | Part Number added                                      |

| 0.13 | Feb. 22, 2012  |                      | Part Number updated                                    |

| 0.14 | Mar. 16, 2012  |                      | Removed Package Drawing for future update              |

| 0.15 | Apr. 26, 2012  | p.3,                 | Changed Block Diagram, Pin out, $1v \rightarrow 1.05v$ |

|      |                | p.5,<br>p.6,<br>p.35 | Added Package Drawing                                  |